## **Instructions:**

• Print your name in the space provided below.

Solution

- This examination is closed book and closed notes, aside from the permitted one-page formula sheet. No calculators or other computing devices may be used. The use of any such device will be interpreted as an indication that you are finished with the test and your test form will be collected immediately.

- Answer each question in the space provided. If you need to continue an answer onto the back of a page, clearly indicate that and label the continuation with the question number.

- If you want partial credit, justify your answers, even when justification is not explicitly required.

- There are 8 questions, some with multiple parts, priced as marked. The maximum score is 100.

- When you have completed the test, sign the pledge at the bottom of this page and turn in the test.

- If you brought a fact sheet to the test, write your name on it and turn it in with the test.

- Note that failing to return this test, or discussing its content with a student who has not taken it, is a violation of the Honor Code.

## Do not start the test until instructed to do so!

| printed                                                                                      |        |  |

|----------------------------------------------------------------------------------------------|--------|--|

|                                                                                              |        |  |

| Pledge: On my honor, I have neither given nor received unauthorized aid on this examination. |        |  |

|                                                                                              |        |  |

|                                                                                              |        |  |

|                                                                                              | signed |  |

Α

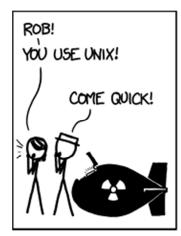

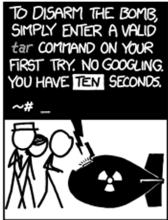

xkcd.com

1. [10 points] Consider the following statement about the MIPS32 datapath design:

The adoption of a pipelined datapath design increases the utilization of the hardware (percentage of the time a unit is actually in use).

Is the statement true or false? Justify your conclusion.

Aside from the interstage buffers and the hardware related to forwarding and hazard detection, all the hardware in the pipeline is also in the single-cycle datapath, and plays the same roles. With the single-cycle datapath, hardware is only busy for a small part of the full clock cycle. For example, the ALU is only in use for a relatively short period of time, certainly no more than 1/5 of the cycle.

OTOH, each stage of the pipeline is busy during each clock cycle (barring execution of a stall). It's true that for certain instructions some hardware will be busy doing irrelevant things, but the same is true with the single-cycle datapath.

Yes, adopting a pipelined design will increase the percentage of the time that most, if not all, datapath components are actually in use.

- 2. Recall how forwarding is employed in the MIPS datapath. Suppose a sequence of instructions is currently in the pipeline; let's label the instructions I1, I2, I3, I4 and I5 and assume they are in WB, MEM, EX, ID and IF respectively.

- a) [6 points] What are the precise conditions in which instruction I4 must receive a forwarded value from the EX/MEM interstage buffer?

There are three instructions ahead of I4 in the pipeline, and I4 will receive a forwarded value when it enters the EX stage. In order for the forwarded value to come from the EX/MEM buffer, it must be written by the instruction that's one stage ahead of I4. So:

I4 receives a value forwarded from EX/MEM iff I3 writes to a register that I4 reads.

b) [6 points] What are the precise conditions in which instruction I3 must receive a forwarded value from the MEM/WB interstage buffer?

Similar to the previous part, except that now the writing instruction must be two stages ahead of the reading instruction, so:

I3 receives a forwarded value from the MEM/WB buffer iff I1 writes to a register that I3 reads AND I2 does not write to the same register (since we would forward to I3 from the EX/MEM buffer).

3. Suppose the following sequence of instructions is executed on the MIPS pipeline:

```

$t0, 0($s1)

# 1

# 2

no dependency

lw

$t1, 4($s1)

$t2, $t1, $t0

# 3 reads $t1 written by #2 (load-use hazard);

add

reads $t0 written by #1

# 4

reads $t2 written by #3 and $t1 written by #2

$s1, $t2, $t1

sub

reads $12 written by #3 and $s1 written by #4

add $s2, $t2, $s1

# 5

reads $s2 written by #5 and $s1 written by #4

$s2, 8($s1)

```

a) [8 points] Would the Hazard Detection Unit take any action with respect to this sequence of instructions? If so, describe exactly what it would do, and why.

As noted above, #3 reads a value written by #2, but #2 is a load instruction, so forwarding alone will not handle the situation.

The Hazard Detection Unit will insert a stall between #2 and #3.

b) [12 points] Assuming any actions described in the previous question have been taken, would the Forwarding Unit ake any action with respect to this sequence of instructions? If so, identify the writing instruction, the reading instruction, the register involved, and which interstage buffer the value would be forwarded from.

With the stall inserted, we must reassess the need for forwarding:

```

$t0, 0($s1)

# 1

lw

$t1, 4($s1)

# 2 no dependency

lw

nop

add

$t2, $t1, $t0

# 3 forward $t1 from MEM/WB; $t0 no issue

$s1, $t2, $t1

# 4 forward $t2 from EX/MEM; $t1 no issue

sub

$s2, $t2, $s1

# 5 forward $t2 from MEM/WB;

add

forward $s1 from EX/MEM

# 6 forward $s2 from EX/MEM and $s1 from MEM/WB

$s2, 8($s1)

SW

```

To sum it all up:

| reader | register                   | source                                              |

|--------|----------------------------|-----------------------------------------------------|

| #3     | <b>\$</b> †1               | MEM/WB                                              |

| #4     | <b>\$</b> †2               | EX/MEM                                              |

| #5     | <b>\$</b> †2               | MEM/WB                                              |

| #5     | <b>\$</b> s1               | EX/MEM                                              |

| #6     | \$s2                       | EX/MEM                                              |

| #6     | <b>\$</b> s1               | MEM/WB                                              |

|        | #3<br>#4<br>#5<br>#5<br>#6 | #3 \$t1<br>#4 \$t2<br>#5 \$t2<br>#5 \$s1<br>#6 \$s2 |

Remember: operands from one stage ahead come from the EX/MEM buffer, operands from two stages ahead come from the MEM/WB buffer, operands from more than two stages ahead do not require forwarding.

4. [8 points] The Hazard Detection Unit essentially turns an instruction into a nop by setting many of the control signals that correspond to the instruction to zero. Could the same result be accomplished by setting just some of those signals to zero? If so, describe a minimal set of control signals that would suffice and explain why. If not, explain why.

What's obviously essential is to render an instruction harmless. No instruction produces output that's directly taken as input by another instruction. Input values are always read from a register or data memory.

So, the Hazard Detection Unit must prevent it from causing anything to be <u>stored</u>, whether in a register or data memory.

However... the instruction should not be allowed to read from an arbitrary memory location, since that could lead to a memory protection error.

The Branch signal might seem to be problematic as well, but the Control unit will always set Branch to 0 in any situation where the Hazard Detection Unit would come into play.

Therefore, it would be sufficient if the Hazard Detection Unit set the following control signals to zero:

RegWrite MemWrite MemRead

5. [10 points] Explain why the pipeline datapath shown in the test supplement does not correctly support execution of beq instructions. Be precise and complete.

The given pipeline design acts on the decision "to branch or not to branch" only when the beq instruction reaches the MEM stage and the AND gate there sets the control signal for the MUX in the IF stage that feeds an instruction address to the PC.

By the time beg has reached the MEM stage, succeeding instructions will have been fetched and will now occupy the EX and ID stages (assume the AND gate acts quickly enough to cause the correct fetch to occur while beg is in MEM).

If the branch IS NOT taken, all is well.

If the branch IS taken, there are two instructions in the pipeline that should have never been fetched, and the given design does not have any way to turn those in to NOP instructions.

**6.** [18 points] A system has 2<sup>40</sup> bytes of DRAM. The system has a single level of cache memory, organized in 2<sup>10</sup> sets each holding 2<sup>8</sup> blocks, with a block size of 2<sup>6</sup> bytes.

Recall that we number bits of an address from low to high, starting at 0: A<sub>n</sub> A<sub>n-1</sub>...A<sub>1</sub>A<sub>0</sub>

How many bits are needed for an address in this system?

2<sup>40</sup> bytes of DRAM implies we need (at least) 40 bits for an address.

Which bits of a DRAM address A would be used to determine the set number to which that address would be mapped?

Since blocks are  $2^6$  bytes, the low six bits ( $A_0$  to  $A_5$ ) are used for byte offsets; since there are  $2^{10}$  sets, set numbers require the next 10 bits:  $A_6$  to  $A_{15}$ .

Which bits of a DRAM address A would be used for the tag field?

The tag consists of the bits not used for byte offsets or set numbers:  $A_{16}$  to  $A_{39}$ .

How many bytes of user (DRAM) data can the cache hold? Express your answer as a power of 2.

$$2^{10} * 2^8 * 2^6 = 2^{24}$$

For a given address, in how many places could the corresponding block of DRAM be stored in the cache?

For a given address, there is only one cache set that could store the corresponding DRAM block. Within that set, there are 2<sup>8</sup> possible locations for the block to be stored.

7. [10 points] Give an example of C code that exhibits spatial locality, and explain why it does.

There are many possible answers; the simplest will involve performing a stride-1 traversal of an array.

- **8.** This question is about the effect of associativity on cache implementation.

- a) [2 points] Which cache design approach implies that for each DRAM address, the corresponding block of data could be stored at a number of locations in the cache, but not just anywhere?

A k-way associative design fits this description.

b) [4 points] Describe the logical conditions that determine whether a particular cache line (block) contains the data matching a particular DRAM address.

There is a match if and only if:

the valid bit for the cache line is 1

**AND**

the tag field of the cache line matches the tag field of the DRAM address

) [6 points] What property of a cache would you change in order to increase the chance of taking advantage of spatial locality? Describe the change precisely, and explain why it would be appropriate.

In order to take advantage of spatial locality, you want the first hit to a sequence of accesses to cause the loading (to the cache) of a significant number of subsequent memory locations.

That implies that you want to choose a larger size for the cache blocks.