## CS 3204 Operating Systems Lecture 17 Godmar Back Virginia <mark>H</mark>Tech

### Announcements

- · Project 2 due tonight

- Reminder: by end of semester, passing students will have provided a deliverable that achieves >= 90% test score on project 2 (or a 100% test score on project 3 or 4's regression

- Additional office hours

- Xiaomo: today 3:00 5:00pm Project 3 Help Sessions

- - Thursday 22<sup>nd</sup> 7-9pm McB 216 Friday 23<sup>rd</sup> 5-7pm McB 216

- Project 3 Design Milestone

- Monday 26th 11:59pm no extensions!

- Midterm March 29

- See announcement + sample midterms on class website

CS 3204 Spring 2007

3/24/2007

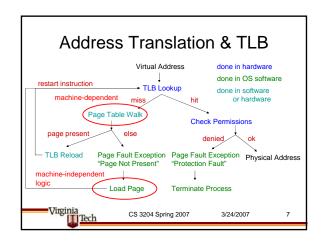

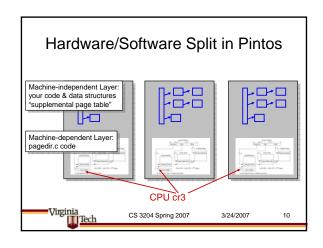

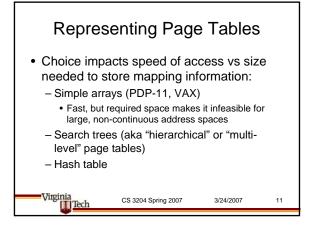

### Implementing Page Tables

- Many, many variations possible

- Done in combination of hardware & software

- Hardware part: dictated by architecture

- Software part: up to OS designer

- Machine-dependent layer that implements architectural constraints (what hardware expects)

- Machine-independent layer that manages page

- Must understand how TLB works first

CS 3204 Spring 2007

3/24/2007

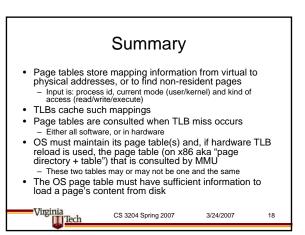

### Page Tables Function & TLB

rans (with paging): Process lds  $\} \times \{$  Virtual Addresses  $\} \times \{$  user, kernel  $\} \times \{$  read, write, execute  $\}$

ightarrow { Physical Addresses }  $\cup$  { INVALID }  $\cup$  { Some Location On Disk

- · For each combination (process id, virtual\_addr, mode, type of access) must decide

- If access is permitted

- If permitted:

- if page is resident, use physical address

- if page is non-resident, page table has information on how to get the page in memory

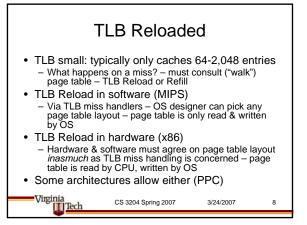

- CPU uses TLB for actual translation page table feeds the TLB on a TLB miss

CS 3204 Spring 2007

3/24/2007

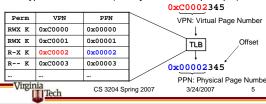

### TLB: Translation Look-Aside Buffer

- Virtual-to-physical translation is part of every instruction (why not only load/store instructions?)

- Thus must execute at CPU pipeline speed

- TLB caches a number of translations in fast, fully-associative memory

- typical: 95% hit rate (locality of reference principle)

### **TLB Management**

- · Note: on previous slide example, TLB entries did not have a process id

- As is true for x86

- · Then: if process changes, some or all TLB entries may become invalid

- X86: flush entire TLB on process switch (refilling adds to cost!)

- Some architectures store process id in TLB entry (MIPS)

- Flushing (some) entries only necessary when process id reused

CS 3204 Spring 2007

3/24/2007

1

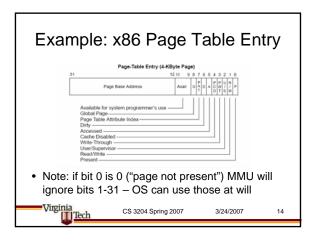

## Page Tables vs TLB Consistency No matter which method is used, OS must ensure that TLB & page tables are consistent On multiprocessor, this may require "TLB shootdown" For software-reloaded TLB: relatively easy TLB will only contain what OS handlers place into it For hardware-reloaded TLB: two choices Use same data structures for page table walk & page loading (hardware designers reserved bits for OS's use in page table) Use a layer on top (facilitates machine-independent implementation) – this is the recommended approach for Pintos Project 3 In this case, must update actual page table (on x86; "page directory") that is consulted by MMU during page table walk Code is already written for you in pagedir.c

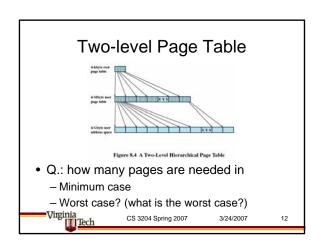

# Example: x86 Address Translation Linear Address 1 22 21 12 11 Directory Table Offset 10 Page Table Offset 1024 PDE + 1024 PTE = 2<sup>10</sup> Pages 32 bits aligned onto a 4-KByte boundary. • Two-level page table • Source: [IA32-v3] 3.7.1 Virginia CS 3204 Spring 2007 3/24/2007 13