# <section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

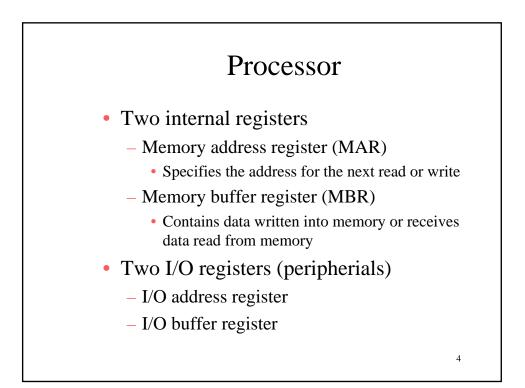

## Control and Status Registers

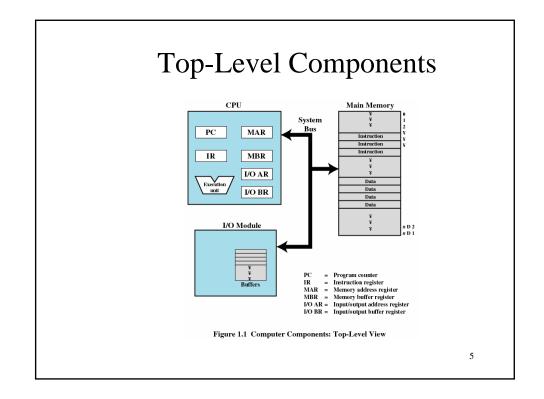

- Program Counter (PC)

- Contains the address of an instruction to be fetched

9

- Instruction Register (IR)

- Contains the instruction most recently fetched

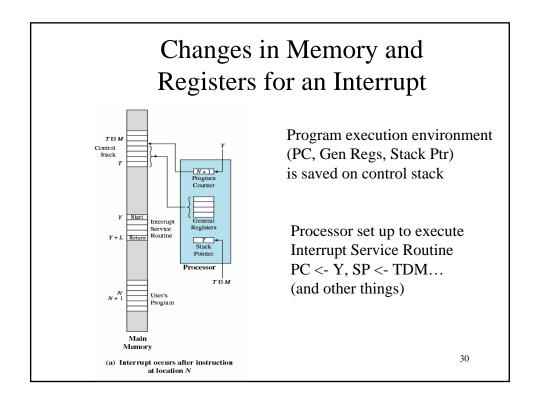

- Program Status Word (PSW)

- Condition codes

- Interrupt enable/disable

- Supervisor/user mode

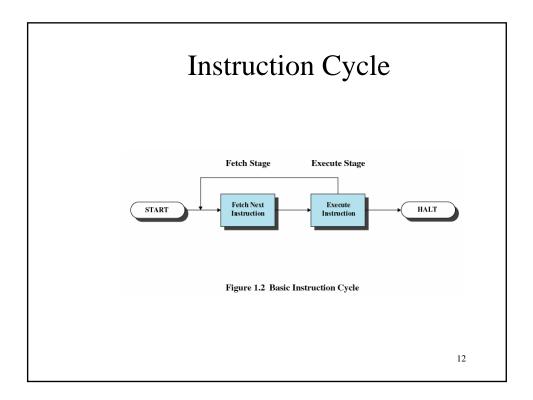

# Instruction Fetch and Execute

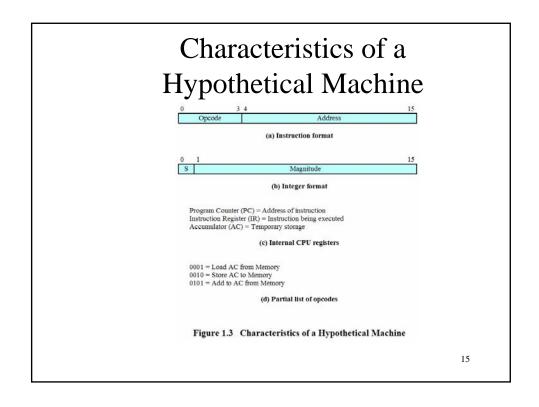

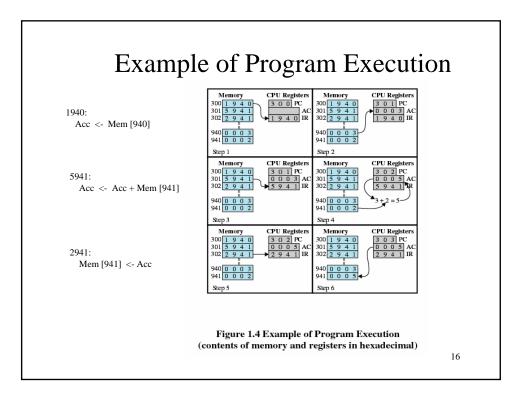

- Program counter (PC) holds address of the instruction to be fetched next

- The processor fetches the instruction from memory

- Program counter is incremented after each fetch

13

<section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

| Classes of Interrupts                   |                                                                                                                                                                                                                                                  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.1         Classes of Interrupts |                                                                                                                                                                                                                                                  |

| 2                                       | Generated by some condition that occurs as a result of an instruction<br>execution, such as arithmetic overflow, division by zero, attempt to execute<br>an illegal machine instruction, and reference outside a user's allowed<br>memory space. |

|                                         | Generated by a timer within the processor. This allows the operating system to perform certain functions on a regular basis.                                                                                                                     |

|                                         | Generated by an I/O controller, to signal normal completion of an operation or to signal a variety of error conditions.                                                                                                                          |

| Hardware failure (                      | Generated by a failure, such as power failure or memory parity error.                                                                                                                                                                            |

# Multiprogramming

- Processor has more than one program to execute

- The sequence the programs are executed depend on their relative priority and whether they are waiting for I/O

- After an interrupt handler completes, control may not return to the program that was executing at the time of the interrupt

35

# Secondary Memory

- Nonvolatile

- Auxiliary memory

- Used to store program and data files

39

# Disk Cache A portion of main memory used as a buffer to temporarily to hold data for the disk Disk read/writes exhibit address clustering Successive/multiple accesses to same data structure or set of instructions (locality) Some data written out may be referenced again. The data are retrieved rapidly from the software cache instead of slowly from disk

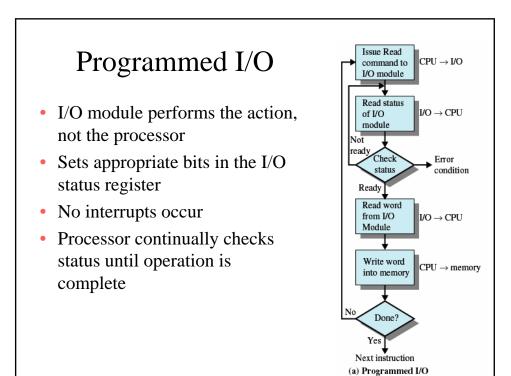

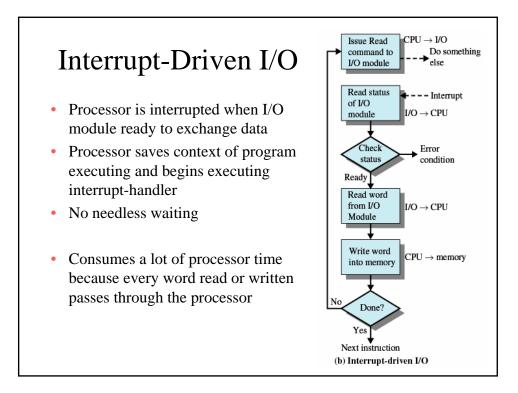

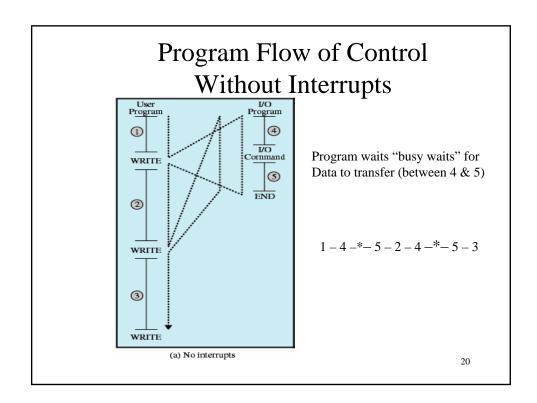

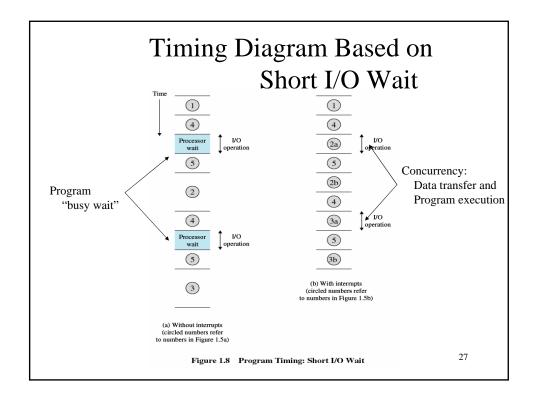

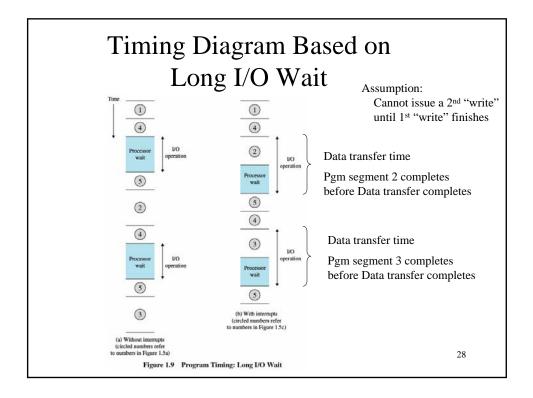

### Approached to Handling I/O (Data Transfer)

- Programmed I/O

- I/O Module performs minimal actions, relies on processor to recognize when I/O complete

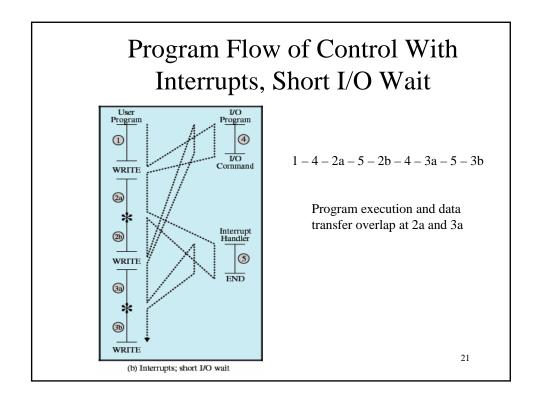

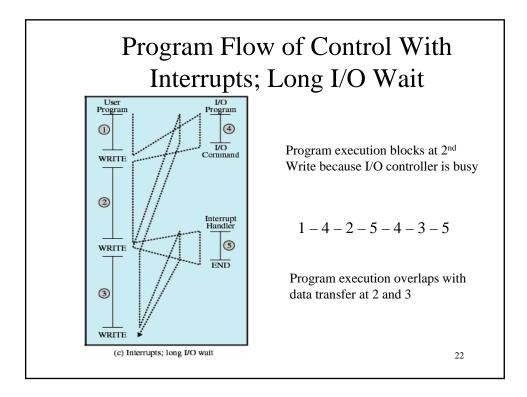

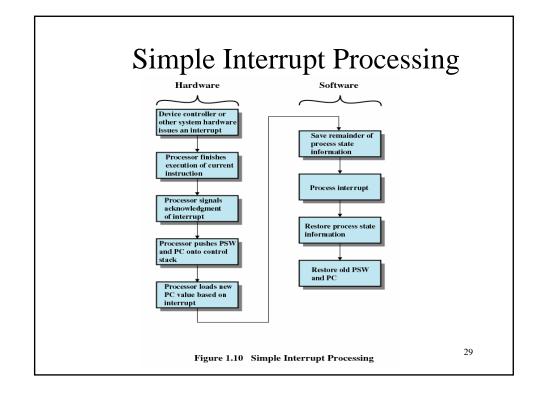

- Interrupt driven I/O

- I/O Module sets interrupt buit

- Overlapping of Pgm execution and data transfer

49

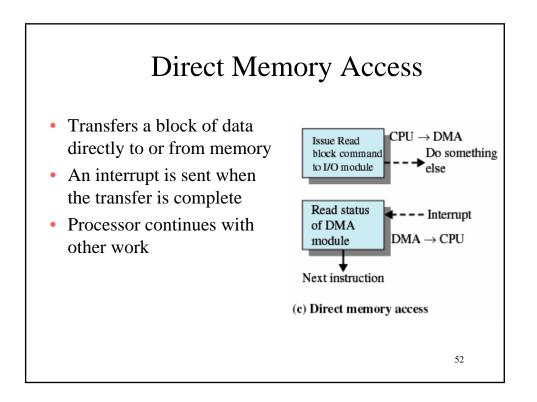

- Direct Memory Access (DMA)

- I/O Module talks directly to Memory Unit