# Chapter 4

# **Computer Organization**

# Machine Language

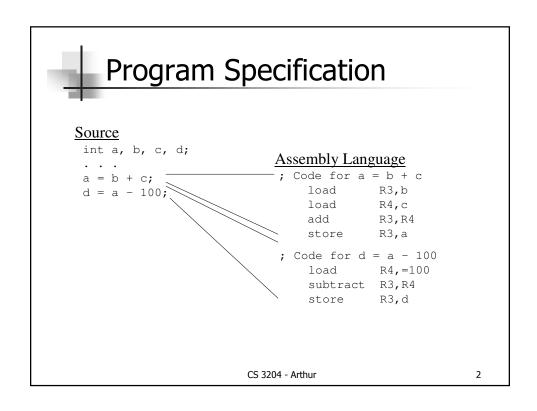

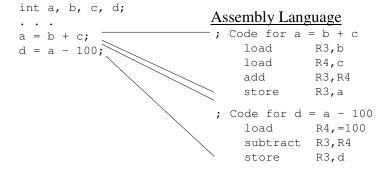

#### Assembly Language

```

; Code for a = b + c

load R3,b

R4,c

load

add R3,R4 store R3,a

; Code for d = a - 100

load R4,=100

subtract R3,R4

store R3,d

```

#### Machine Language

| 1011110010011001 |

|------------------|

| 101110010100000  |

| 101001110011000  |

| 101110100011001  |

| 101110010100000  |

| 101001100011000  |

| 101110011011001  |

CS 3204 - Arthur

3

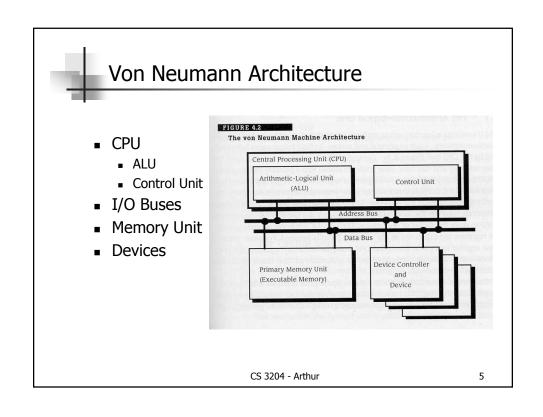

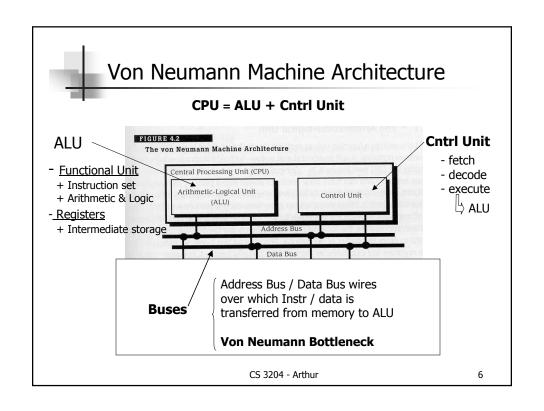

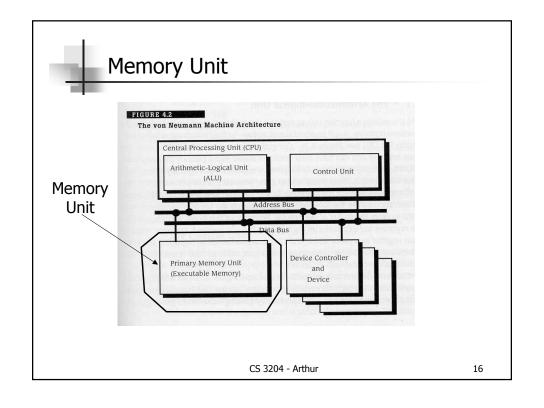

### Von Neumann Concept

- Stored program concept

- General purpose computational device driven by internally stored program

- Data and instructions look same i.e. binary

- Operation being executed determined by HOW we look at the sequence of bits

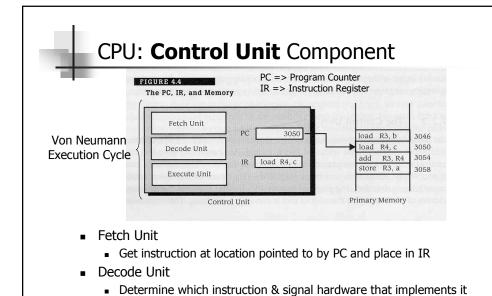

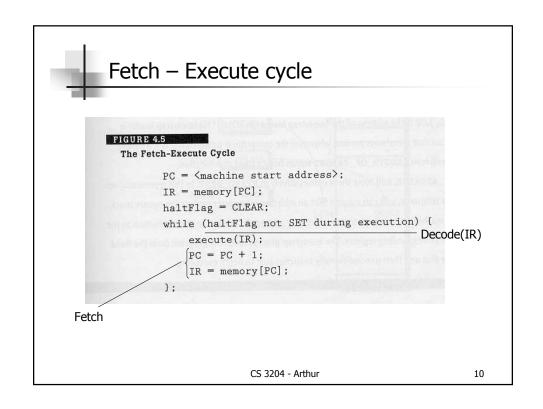

- **Fetch** View bits as instruction Decode Execute

**<u>Data</u>** might be fetched as a result of execution

CS 3204 - Arthur

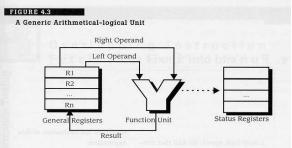

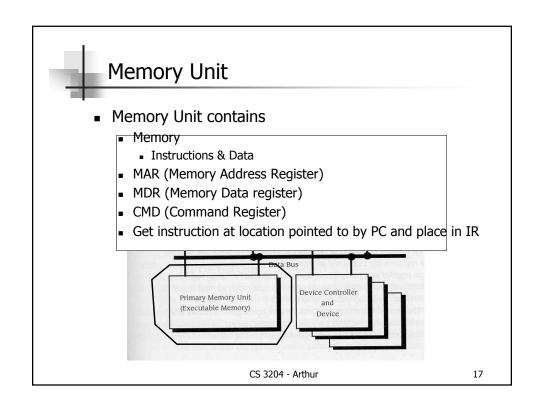

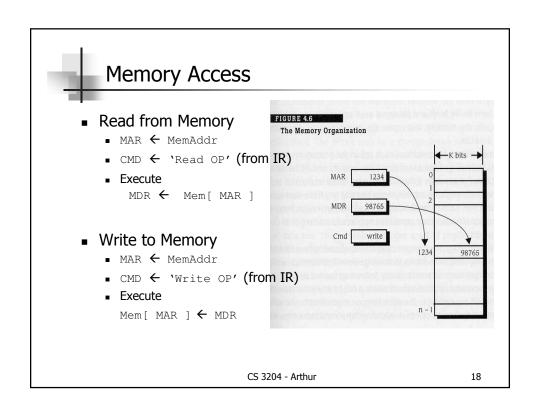

# CPU: **ALU** Component

- Assumes instruction format: OP code, LHO, RHO

- Instruction / data fetched & placed in register

- Instruction / data retrieved by functional unit & executed

- Results placed back in registers

- Control Unit sequences the operations

CS 3204 - Arthur

7

# Program Specification (revisited)

#### Source

CS 3204 - Arthur

- Determine which instruction a signal hardware the

- Execute Unit

- Hardware for instruction execution (could cause more data fetches)

CS 3204 - Arthur

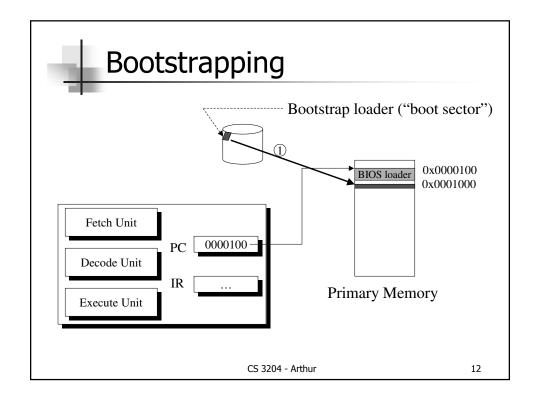

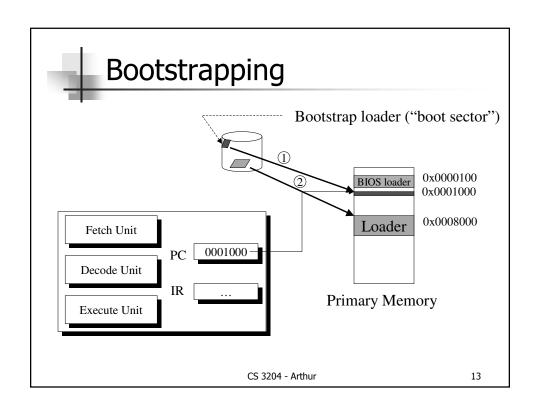

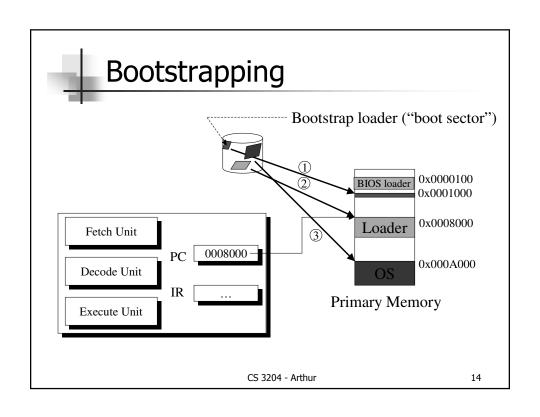

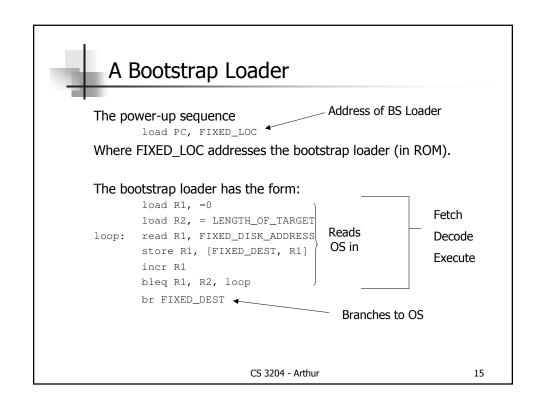

## OS boot-up...

- How does the system boot up?

- Bootstrap loader

- OS

- Application

CS 3204 - Arthur

### How do interrupts factor in?

- Scenario (1)

- Program:

```

while device_flag busy {}

```

- => Busy wait consumes CPU cycles

- Scenario (2)

- Program:

```

while (Flag != write) {

sleep( X )

}

```

=>If write available while program sleeping - inefficient

CS 3204 - Arthur

## How do interrupts factor in ? ...

- Scenario (3)

- Program:

issues "write"

#### Driver:

- Suspend program until write is completed,

then program is unsuspended

- This is Interrupt-driven

CS 3204 - Arthur

25

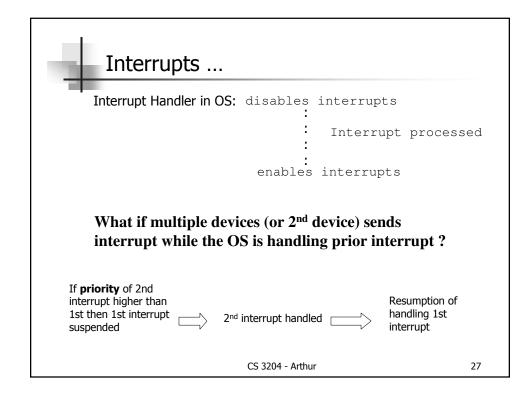

#### Interrupts Driven Service Request

- Process is suspended only if driver/controller/device cannot service request

- If a process is suspended, then, when the suspended process' service request can be honored

- Device interrupts CPU

- OS takes over

- OS examines interrupts

- OS un-suspends the process

- Interrupts

- Eliminate busy wait

- Minimizes idle time

CS 3204 - Arthur

### Control Unit with Interrupt (H/W)

```

PC = <machine start address>;

IR = memory[PC];

haltFlag = CLEAR;

while(haltFlag not SET) {

execute(IR);

PC = PC + sizeof(INSTRUCT);

IR = memory[PC];

if(InterruptRequest) {

memory[0] = PC;

PC = memory[1]

};

```

memory[1] contains the address of the interrupt handler

CS 3204 - Arthur

) Q

### Interrupt Handler (Software)

```

interruptHandler() {

saveProcessorState();

for(i=0; i<NumberOfDevices; i++)

if(device[i].done) goto deviceHandler(i);

/* something wrong if we get to here ... */

deviceHandler(int i) {

finishOperation();

returnToScheduler();

}</pre>

```

CS 3204 - Arthur

29

#### A Race Condition

```

saveProcessorState() {

for(i=0; i<NumberOfRegisters; i++)</pre>

memory[K+i] = R[i];

for(i=0; i<NumberOfStatusRegisters; i++)</pre>

memory[K+NumberOfRegisters+i] = StatusRegister[i];

PC = <machine start address>;

IR = memory[PC];

haltFlag = CLEAR;

while(haltFlag not SET) {

execute(IR);

PC = PC + sizeof(INSTRUCT);

IR = memory[PC];

if(InterruptRequest && InterruptEnabled) {

disableInterupts();

memory[0] = PC;

PC = memory[1]

};

CS 3204 - Arthur

```

#### Revisiting the trap Instruction (H/W)

```

executeTrap(argument) {

setMode(supervisor);

switch(argument) {

case 1: PC = memory[1001]; // Trap handler 1

case 2: PC = memory[1002]; // Trap handler 2

. . .

case n: PC = memory[1000+n];// Trap handler n

};

```

- The trap instruction dispatches a trap handler routine atomically

- Trap handler performs desired processing

- "A trap is a software interrupt"

CS 3204 - Arthur

31

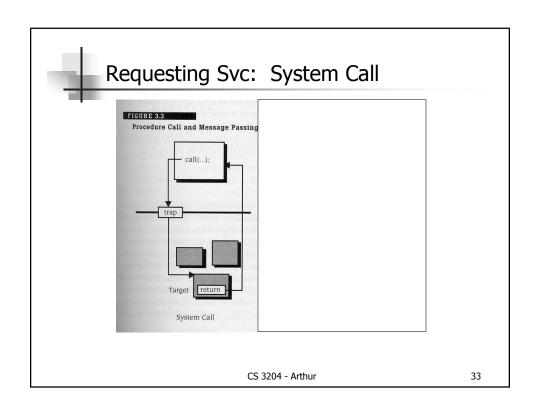

#### Requesting Service from OS

Kernel functions are invoked by "trap"

- System call

- Process traps to OS Interrupt Handler

- Supervisor mode set

- Desired function executed

- User mode set

- Returns to application

CS 3204 - Arthur