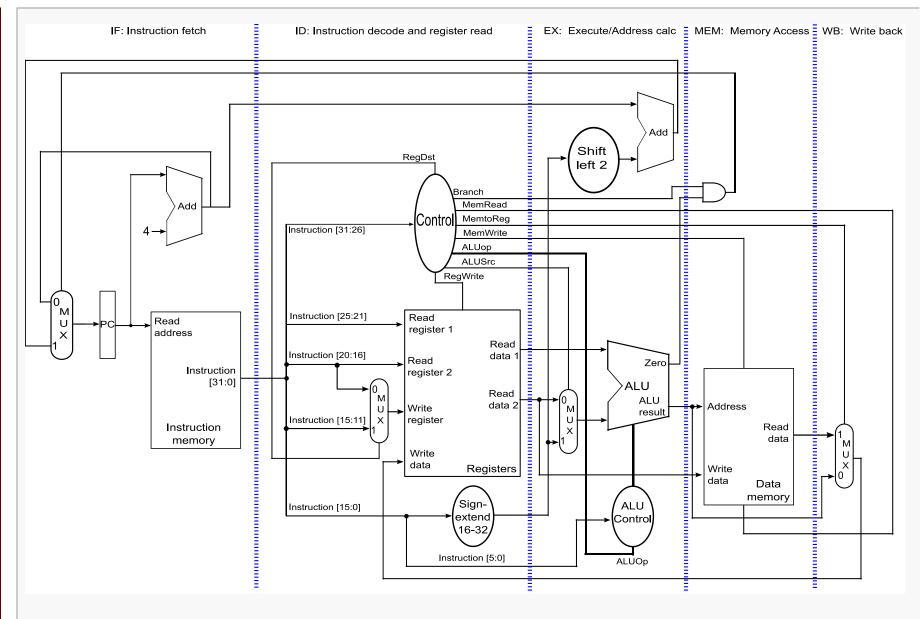

# **Current Design**

## Synchronizing 1

CS@VT

#### **Computer Organization II**

## Consider executing:

| add | \$t2, | \$t1,   | \$t0 |

|-----|-------|---------|------|

| sub | \$t3, | \$t1,   | \$t0 |

| or  | \$t4, | \$t1,   | \$t0 |

| SW  | \$t2, | 0(\$t0) |      |

- # needs MemWrite = 0

- # needs MemWrite = 0

- # needs MemWrite = 0

- # needs MemWrite = 1

### **Computer Organization II**

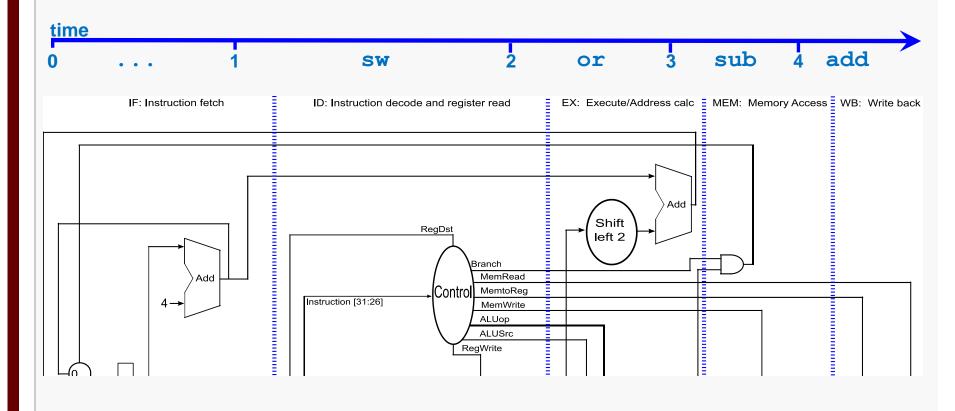

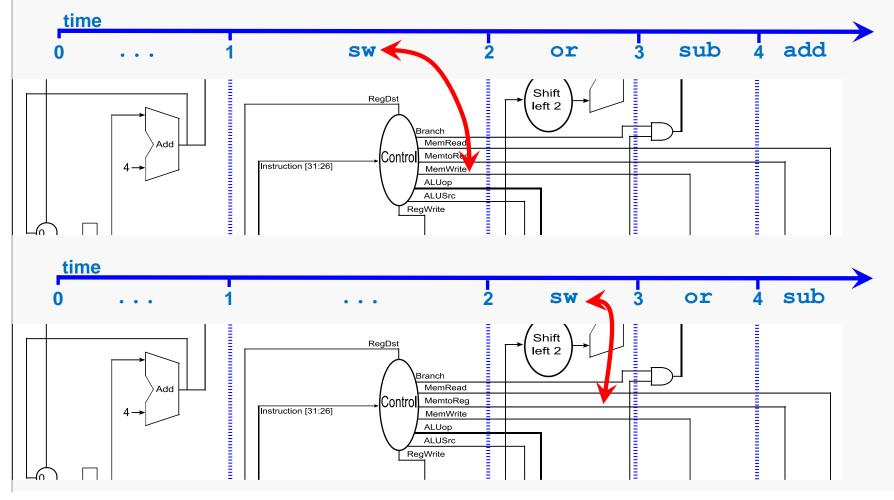

Synchronizing 3

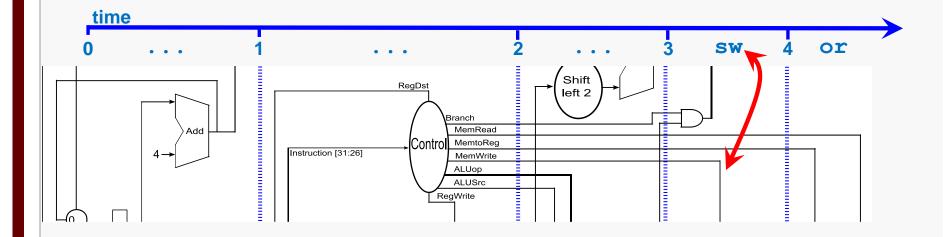

What happens during cycle 4? Among other things...

- sw reaches the ID stage, and Control sets MemWrite to 1

- so, a memory write will occur while sub is in the MEM stage

- and that's bad news...

### **Computer Organization II**

What needs to happen instead?

- the value of MemWrite that goes with sw...

- ... needs to travel forward, stage to stage as sw does

CS@VT

## **Computer Organization II**

#### ©2005-2020 WD McQuain

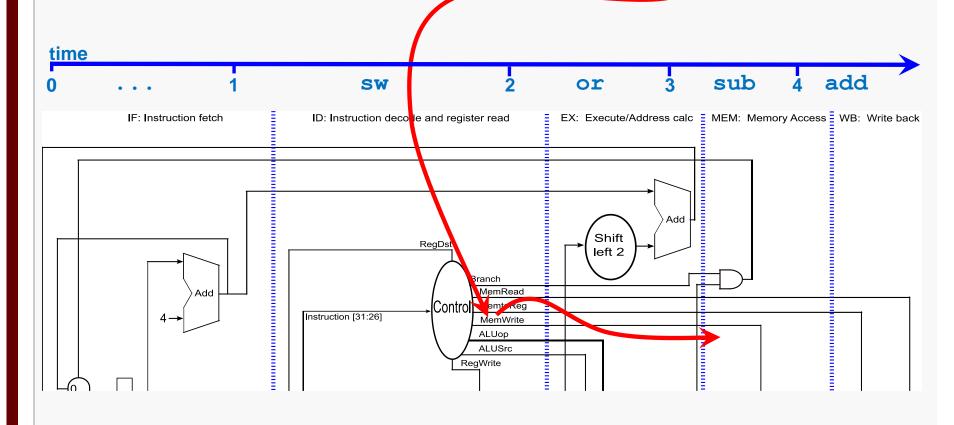

Synchronizing 4

What needs to happen instead?

- the value of MemWrite that goes with sw...

- ... needs to travel forward, stage to stage as sw does

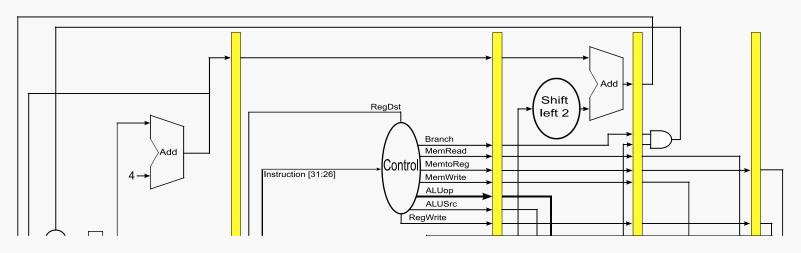

So how do we make this happen?

**Computer Organization II**

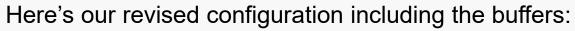

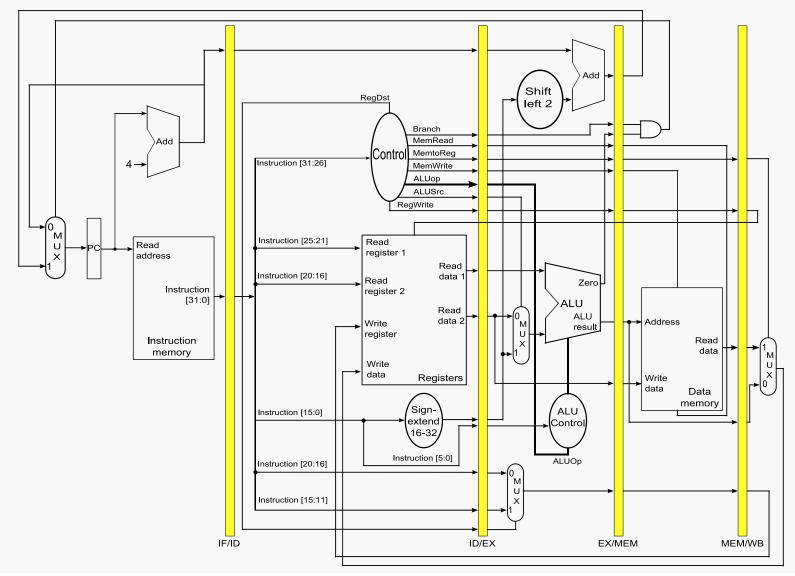

## **Adding Buffers**

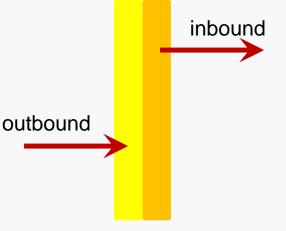

Put storage buffers between adjacent stages:

Control writes/reads on these buffers with the clock signal. Read values entering a stage from the "inbound" buffer. Write values exiting a stage to the "outbound" buffer.

So no signal (or data value) arrives before its time...

**Computer Organization II**

We have an idea: put buffers between adjacent stages and use those buffers to synchronize the operation of the pipeline stages

Are we sure we are handling all control signals properly... for every instruction?

Are there any values, other than control signals that must be passed through the interstage buffers?

Signals and values:

- may move forward (from lower-numbered to higher-numbered stages)

- can they ever move backward?

- should they ever bypass the interstage buffers?

We will pick a particular instruction and consider its execution in detail...

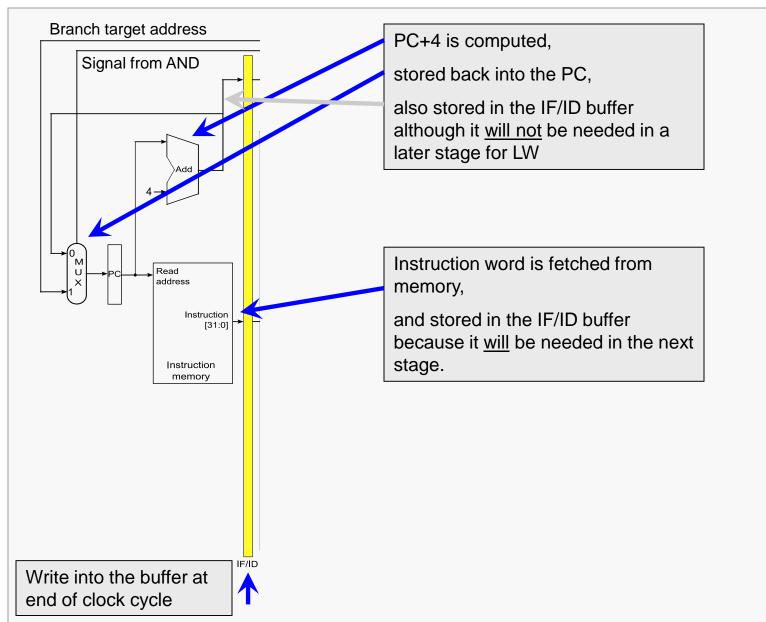

# IF Stage for LW

#### CS@VT

## **Computer Organization II**

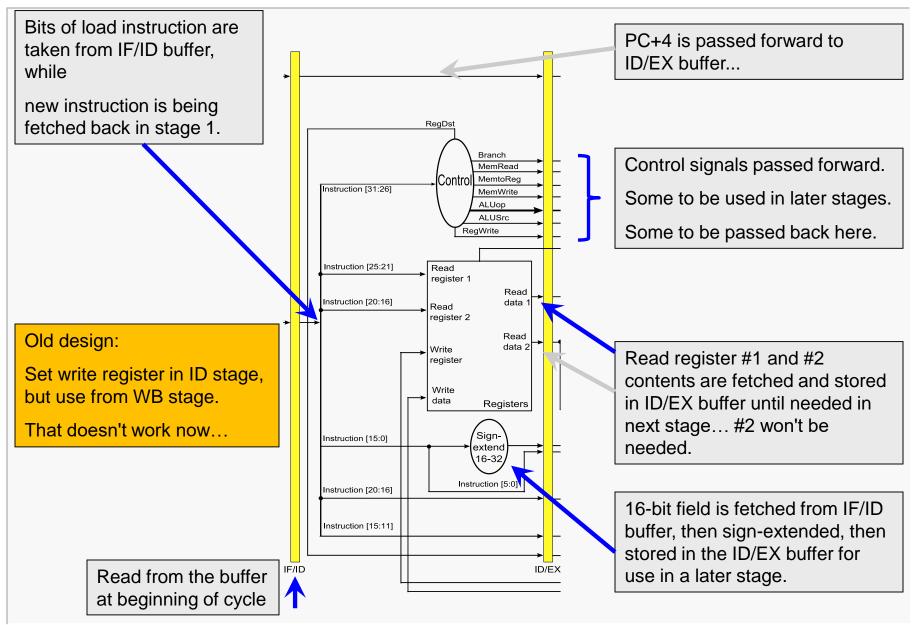

# ID Stage for LW

#### CS@VT

### **Computer Organization II**

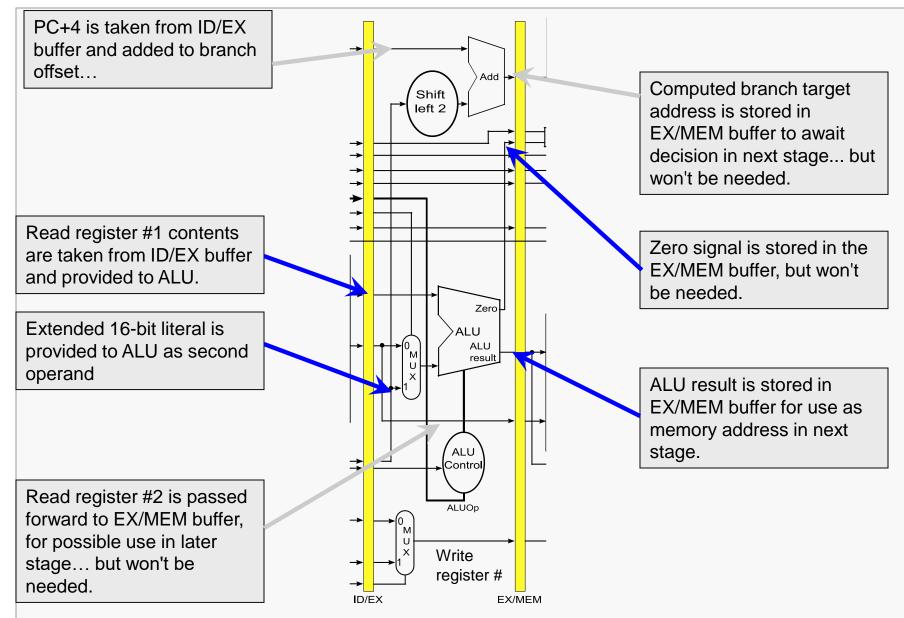

## EX Stage for LW

#### CS@VT

### **Computer Organization II**

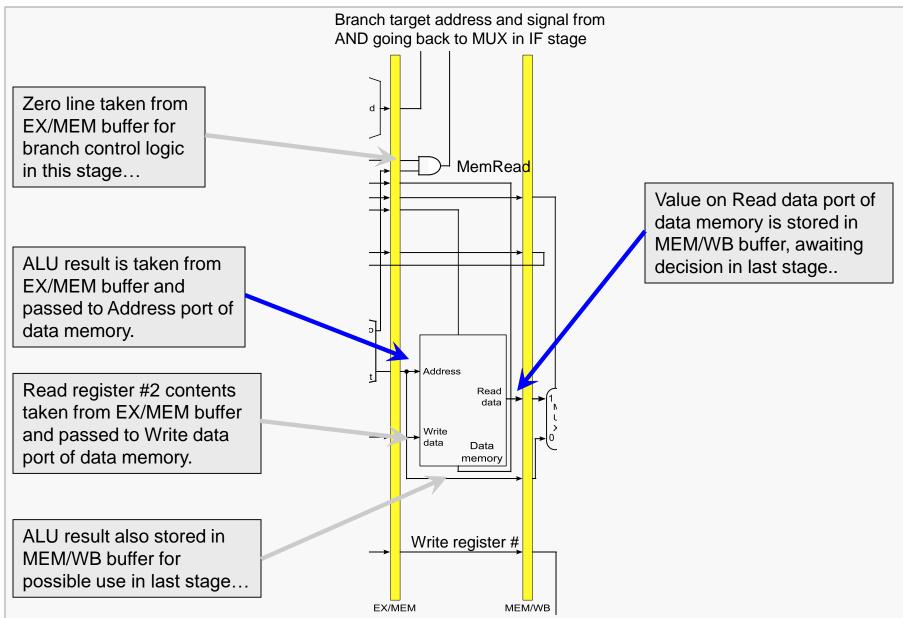

# MEM Stage for LW

#### CS@VT

### **Computer Organization II**

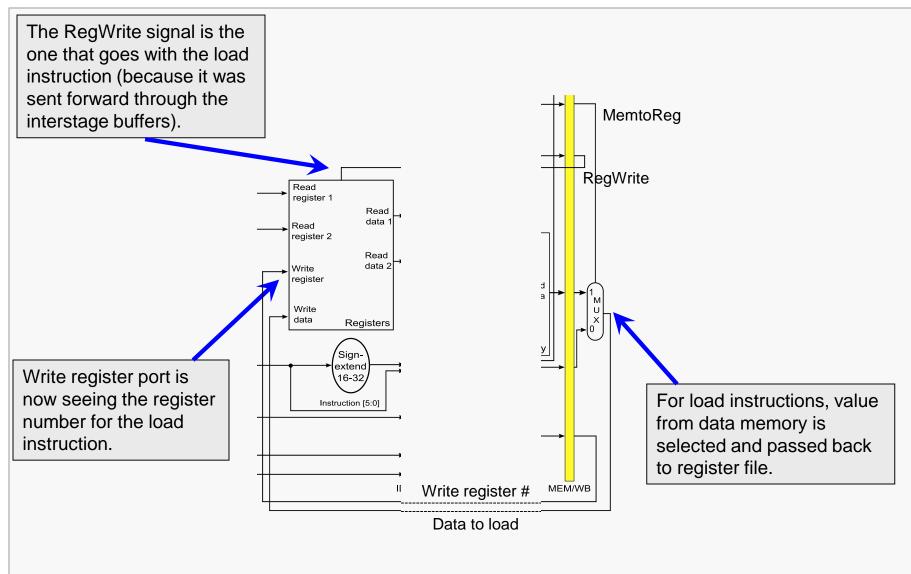

## WB Stage for LW

#### CS@VT

### **Computer Organization II**

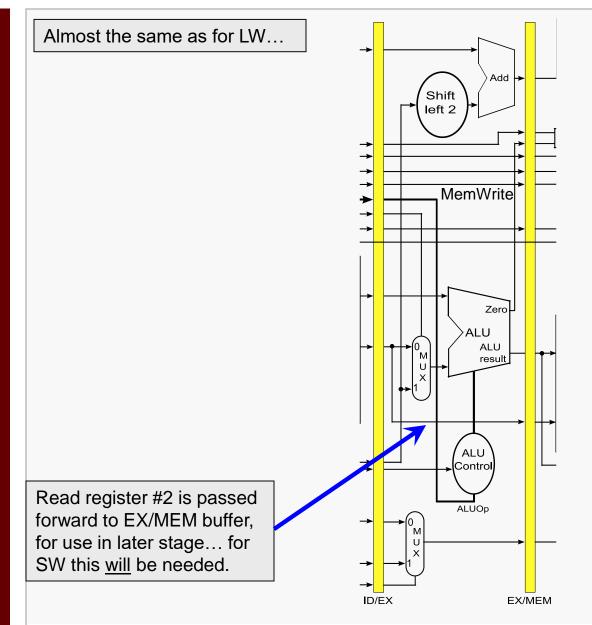

# **Current Design**

CS@VT

### **Computer Organization II**

## What now?

Would considering the execution of a different instruction yield new insights?

We will consider a similar instruction next: SW

Now, the IF stage is the same for all instructions, so we'll ignore it.

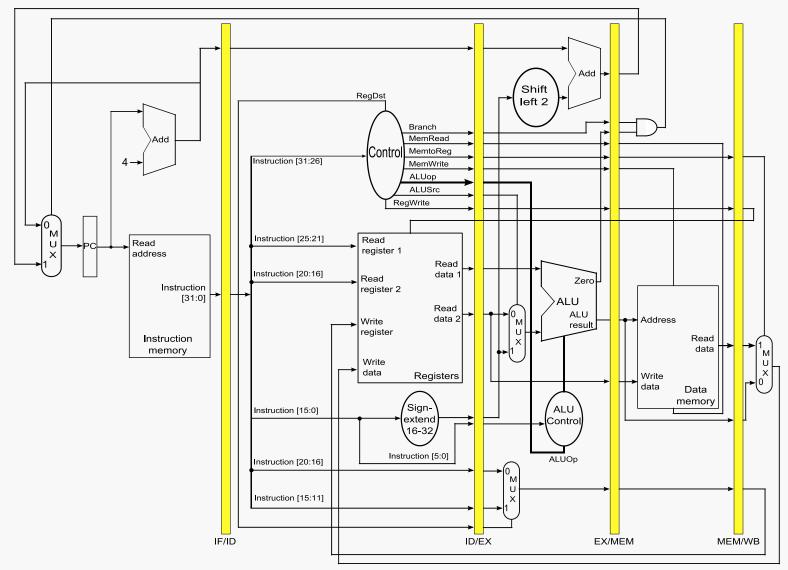

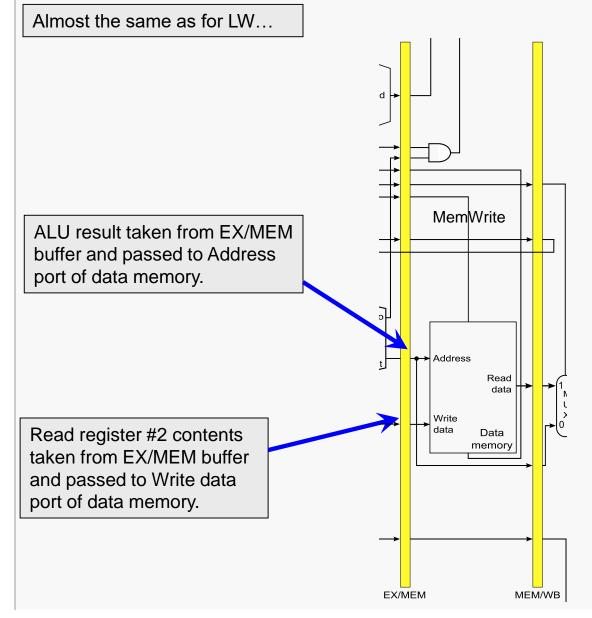

## EX Stage for SW

#### CS@VT

## **Computer Organization II**

# MEM Stage for SW

#### CS@VT

### **Computer Organization II**

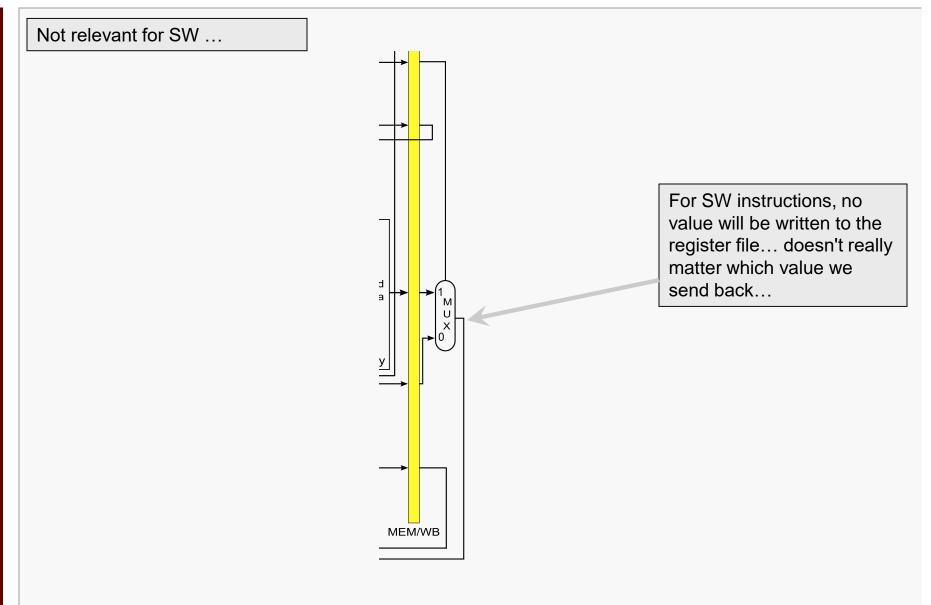

## WB Stage for SW

## **Computer Organization II**

Can you repeat this analysis for other sorts of instructions, identifying in each stage what's relevant and what's not?

How much storage space does each interstage buffer need? Why?

Could adding interstage buffers affect the clock cycle? Why?

**Computer Organization II**

# Summary

## Here's our preliminary configuration for the buffers:

CS@VT

### **Computer Organization II**